Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

2024-04-01

Gegenwärtig sind die Servomotoren in den inländischen CNC -Werkzeugen im Allgemeinen mit inkrementellen Encodern ausgestattet, während die Genauigkeit inkrementeller Encoder nicht zu hoch ist und die Ausgabe parallelen Signalen ist. Um seine Genauigkeit zu verbessern, ist es notwendig, das Design des Encoders zu erhöhen. Schwierigkeiten und erhöhen Sie die Ausgabe paralleler Signale, die der Fernkommunikation zwischen der Servoeinheit und dem Encoder nicht förderlich sind. Der absolute Encoder wird verwendet, außer dass seine Genauigkeit mehrmals höher ist als der des inkrementellen Encoders. Die serielle Hochgeschwindigkeitskommunikation spart Kommunikationslinien für die Fernkommunikation mit Ferngeschwindigkeit. Am anderen Ende des Encoders werden CPLD und Absolute-Encoder für die serielle Hochgeschwindigkeitskommunikation verwendet. Die CPLD wandelt dann die empfangenen Encoderinformationen in parallele Datenübertragung um. Die DSP in der Servoeinheit führt die arithmetische Kontrolle durch. In diesem Artikel wird das Software- und Hardware-Design der seriellen Hochgeschwindigkeitskommunikation zwischen CPLD und absolutem Encoder verleiht.

Hardwaredesign

Die Hardware besteht hauptsächlich aus drei Modulen: Stromversorgung, CPLD und ihre peripheren Schaltungen und der absolute Encoder -Grenzflächenschaltung.

Leistungsmodul

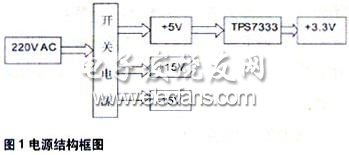

Das Leistungsmodul besteht aus einem Schaltnetzteil und einem DC/DC -Stromversorgungschip, wie in Abbildung 1 gezeigt.

Die Schaltnetzversorgung in der Abbildung wandelt die 220 -V -Wechselstromnetzspannung in +5 V, +15 V, -15 V um. Die Schaltnetzversorgung kann verschiedene Interferenzen im Stromnetz herausfiltern, und der Transformator in der Schaltnetzversorgung beträgt 220 V AC und der Ausgang beträgt + 5 V, + 15 V, -15 V, der interne Schaltkreis verwendet auch TL431, um die Einstellung der Einstellung des Leitungsimpulsbreite des Schaltschlauchs, so dass die Anti-Interferenz-, Sicherheit, Stabilitäts- und Spannungsregulation der Schaltnetzversorgung besser ist. Der TPS7333 ist ein DC/DC -Chip. Die +5V -Gleichspannung wird in eine stabile Gleichspannung von +3,3 V für die Verwendung durch die CPLD umgewandelt. Der TPS7333 hat eine bessere Umwandlungseffizienz, Zuverlässigkeit und Spannungsregulierung. Es kann im Spannungsbereich von +3,77 V- +10 V verwendet werden. Durch die Umwandlung +3,3 V brennt die CPLD aus, da die Eingangsspannung zu hoch ist.

CPLD und seine peripheren Schaltungsmodule

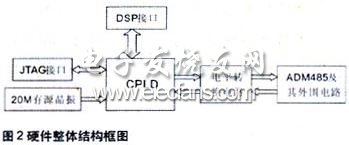

Die CPLD und ihre peripheren Schaltungsmodule bestehen hauptsächlich aus CPLD, CPLD -Programmier -Download -Grenzflächenschaltung (JTAG -Schnittstelle), DSP -Grenzflächenschaltung, aktivem Kristalloszillator, Pegelkonvertierungsschaltung und ADM485 und ihren peripheren Schaltkreisen (Grenzfläche für die Kommunikation mit dem Codierer) . Figur 2).

Diese Design -CPLD verwendet den EPM570T144C5 von Altera, das zu Alteras Max II gehört. Max II ist niedriger als max I und verbraucht weniger Strom. Das Gerät verfügt über mehr Makrozellen und die Geräteverzögerung wird innerhalb von 6 ns gesteuert. Mit hoher Kostenleistung verfügt der EPM570T144C5 über 570 Makrozellen. Die Anzahl der Stifte am Chip beträgt 144, von denen 116 E/A -Ports verfügbar sind, sodass die Ressourcen dieses Chips ausreichend sind. Die CPLD ist hauptsächlich für die Hochgeschwindigkeits-serielle Kommunikation mit dem absoluten Encoder verantwortlich und wird vom DSP-Befehl gesteuert, um die Encoder-Daten und andere Informationen parallel an den DSP weiterzuleiten.

Die JTAG -Schnittstelle wird hauptsächlich zum Herunterladen der ausführbaren Datei in die CPLD verwendet, die Entwicklungsumgebung des Altera Company - Quartus II auf dem PC installiert und das schriftliche VHDL -Programm in dieser Entwicklungsumgebung erfasst, um sicherzustellen, dass die Kompilierung nicht fehlerfrei ist und die Funktion wird implementiert. Schließen Sie das Download -Kabel an die JTAG -Schnittstelle an und laden Sie das CPLD -Board über das von Quartus II bereitgestellte Programmdownload -Tool herunter.

Die DSP -Schnittstelle besteht aus 8 Datenlinien, 3 Adresslinien und 1 Steuerlinie. Die 8 Datenlinien sind für die Übertragung der Encoder -Daten und anderer Informationen verantwortlich. Die 3 Adressleitungen sind für die Übertragung von DSP -Befehlen und die Dekodierung am CPLD -Terminal verantwortlich. Die CPLD überträgt die Encoder -Daten oder andere Informationen über 8 Datenzeilen gemäß dem dekodierten Befehl an die DSP. Die Kontrolllinie vervollständigt hauptsächlich die synchrone Steuerung der CPLD und des DSP.

Der 20 m aktive Kristalloszillator bietet hauptsächlich eine Referenzuhr für die CPLD. Unter dem Fahren des Taktsignals erzeugt die CPLD eine Baudrate von 2,5 MB/s, um mit dem Encoder zu kommunizieren, und erzeugt einen 10 -M -Hz -Takt für einige Logiksteuerungssignale. Die Bereitstellung einer Taktfrequenz von 20 m Hz erfordert eine 3,3 -V -Gleichstromspannung aus der Stromversorgung.

Der Levelwechselkreis ist hauptsächlich für die Umwandlung von 3,3 V in 5 V oder 5 V in 3,3 V verantwortlich, da die Kern- und E/A -Anschlüsse der CPLD eine Versorgungsspannung von 3,3 V erfordern, die für ADM485 und Absolute -Encoder erforderlich ist. Sowohl die Versorgungsspannung als auch die E/A -Anschluss -Treiberschaltung sind 5 V. Daher müssen 3,3 V oder 5 V mit dem Level Conversion Chip LVC4245A in 5 V oder 5 V in 3,3 V konvertiert werden.

ADM485 und seine peripheren Schaltkreise sind die Hardware-Verbindung zwischen CPLD und absoluter Hochgeschwindigkeitskommunikation. Die Arbeitsspannung von ADM485 beträgt 5 V und ihre maximale Kommunikationsgeschwindigkeit beträgt 5 MB/s. Die Verwendung von zwei ADM485-Chips zum Docking-Kommunikation kann die Fähigkeit zur Anti-Interferenz auf der Kommunikationslinie verbessern, und die längste Übertragungsabstand kann 1,2 km erreichen. Die periphere Schaltung ist in Abbildung 3 dargestellt. Die rechte Hälfte der gepunkteten Linie gehört zum peripheren Schaltkreis des absoluten Encoders. Die Pull-up- und Pulldown-Widerstände sind 1 km Ohm, der aktuelle limitierende Widerstand beträgt 220 Ohm und der ADM485-SDAT ist der Datenausgangspin. ADM485 IS SRQ ist der Dateneingangspin, DE von ADM485 ist der externe Kontrollstift, dieser Pin wird von CPLD gesteuert. Da das RS-485-Kommunikationsprotokoll Half Duplex ist, kann ADM485 nur im Zustand des Sendens von Daten oder beim Empfangen von Daten sein. Wenn ADM485 de hoch ist, befindet sich ADM485 im Datenausgangszustand (dh CPLD erhält Daten). Wenn DE von ADM485 niedrig ist, befindet sich ADM485 im Dateneingabestatus (dh CPLD sendet Daten).

Aufteilen:

Anfrage versenden

Ms. carol Dong

Telefonnummer:86-431-85543703

Fax:86-431---88634119

Mobiltelefon:+8613894866263

E-Mail-Adresse:sales@encoders.com.cn

Firmenadresse:333Feiyue Donglu, Changchun City, Jilin Province. China, Changchun, Jilin

Mobile Seite

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.